2023年9月6日(水)

『 RISC-V 』をFPGAに実装しました!

近年、各ベンダーのFPGAに使用される『RISC-V』(オープンな命令セットアーキテクチャ)を、

フルスクラッチして評価基板で動作させてみました。

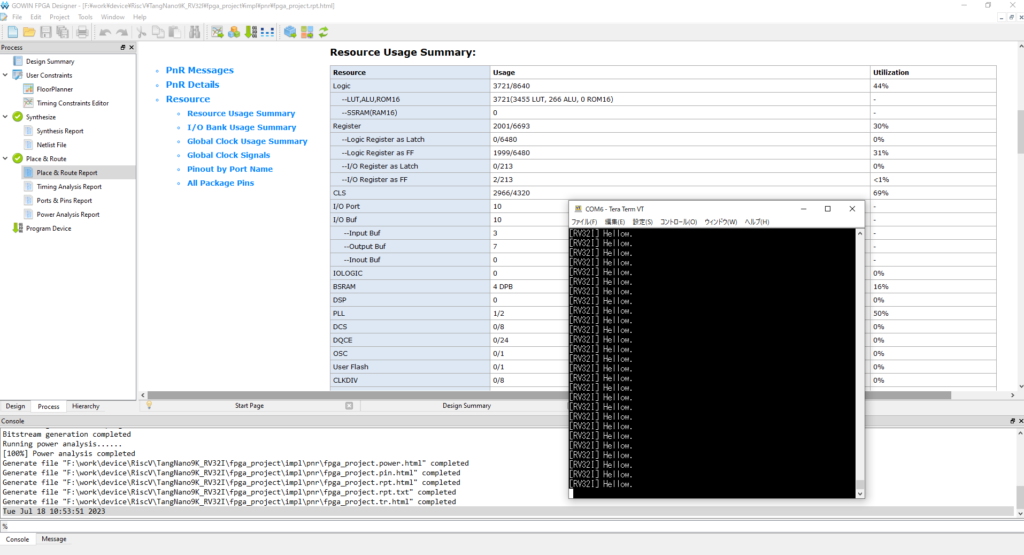

今回作成のRISC-Vは、基本の『RV32I』(拡張機能無し)の5段パイプライン構成とし、言語は

Verilog-HDLを使用。内部バスにはAXI4-Liteで、自作のUARTとGPIO(LED制御)ブロックに

接続し、1秒間隔でLEDを点灯させ、UARTに文字列を出力するデザインとなっています。

ソフトはEclipseにRISC-Vのクロスコンパイラを導入し、C言語からバイナリコードを生成、

そのバイナリコードをpythonでASCIIのhexコードに変換し、命令メモリの初期値として

与えてみました。

以下は開発の様子と、UARTの接続画面となります。

引き続き評価を進めながら、動作理解を進めて行きます!

※使用基板 : TangNano9K(GowinのFPGAが使用されているUSBメモリサイズの評価基板です)

お問合せはこちらまで

sys-ip@systec.co.jp

We have tried to make “RISC-V” (open instruction set architecture), which is used in FPGAs from various vendors in recent years, fully scratch and run on an evaluation board.

The RISC-V created this time has a basic “RV32I” (no extensions) 5-stage pipeline configuration and uses Verilog-HDL as the language. The internal bus is AXI4-Lite, connected to a home-made UART and GPIO (LED control) block, and the design turns on LEDs at 1-second intervals and outputs strings to the UART.

The software was created by installing a RISC-V cross-compiler in Eclipse, generating binary code from C, converting the binary code to ASCII hex code in python, and then using it as the initial value of the instruction memory. The binary code was converted to ASCII hex code by python and given as the initial value of instruction memory.

=>The board used : TangNano9K (USB memory size evaluation board with Gowin’s FPGA)